Ayhan, Tuba

Loading...

Profile URL

Name Variants

Ayhan T.

Job Title

Email Address

ayhant@mef.edu.tr

Main Affiliation

02.05. Department of Electrical and Electronics Engineering

Status

Current Staff

Website

ORCID ID

Scopus Author ID

Turkish CoHE Profile ID

Google Scholar ID

WoS Researcher ID

Sustainable Development Goals

1

NO POVERTY

0

Research Products

3

GOOD HEALTH AND WELL-BEING

1

Research Products

8

DECENT WORK AND ECONOMIC GROWTH

0

Research Products

9

INDUSTRY, INNOVATION AND INFRASTRUCTURE

1

Research Products

10

REDUCED INEQUALITIES

0

Research Products

6

CLEAN WATER AND SANITATION

0

Research Products

5

GENDER EQUALITY

0

Research Products

17

PARTNERSHIPS FOR THE GOALS

0

Research Products

11

SUSTAINABLE CITIES AND COMMUNITIES

0

Research Products

2

ZERO HUNGER

0

Research Products

16

PEACE, JUSTICE AND STRONG INSTITUTIONS

0

Research Products

12

RESPONSIBLE CONSUMPTION AND PRODUCTION

0

Research Products

14

LIFE BELOW WATER

0

Research Products

15

LIFE ON LAND

0

Research Products

4

QUALITY EDUCATION

0

Research Products

13

CLIMATE ACTION

0

Research Products

7

AFFORDABLE AND CLEAN ENERGY

1

Research Products

Documents

29

Citations

734

h-index

7

Documents

20

Citations

652

Scholarly Output

10

Articles

0

Views / Downloads

2042/7940

Supervised MSc Theses

1

Supervised PhD Theses

0

WoS Citation Count

3

Scopus Citation Count

19

WoS h-index

1

Scopus h-index

2

Patents

0

Projects

5

WoS Citations per Publication

0.30

Scopus Citations per Publication

1.90

Open Access Source

4

Supervised Theses

1

| Journal | Count |

|---|---|

| 2023 30th IEEE International Conference on Electronics, Circuits and Systems (ICECS) | 2 |

| 2021 13th International Conference on Electrical and Electronics Engineering (ELECO) | 1 |

| 2021 29th Signal Processing and Communications Applications Conference (SIU) | 1 |

| 2020 28th Signal Processing and Communications Applications Conference (SIU) | 1 |

| 21st International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design-SMACD -- JUL 07-10, 2025 -- Istanbul, TURKIYE | 1 |

Current Page: 1 / 2

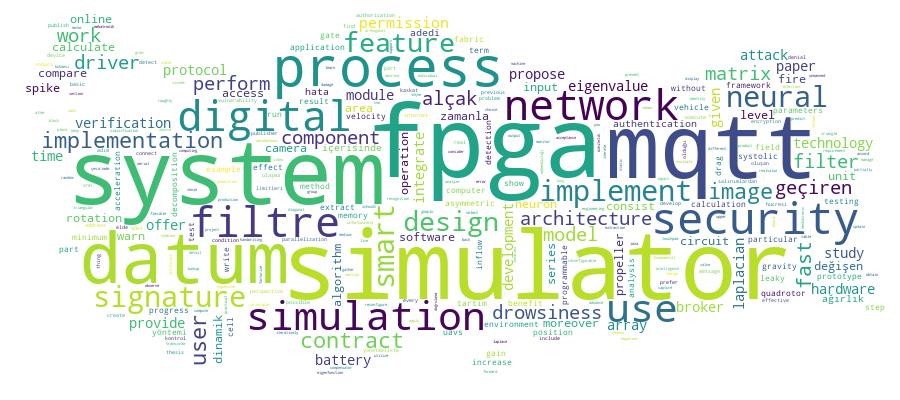

Competency Cloud